ASIC, FPGA and Embedded Systems

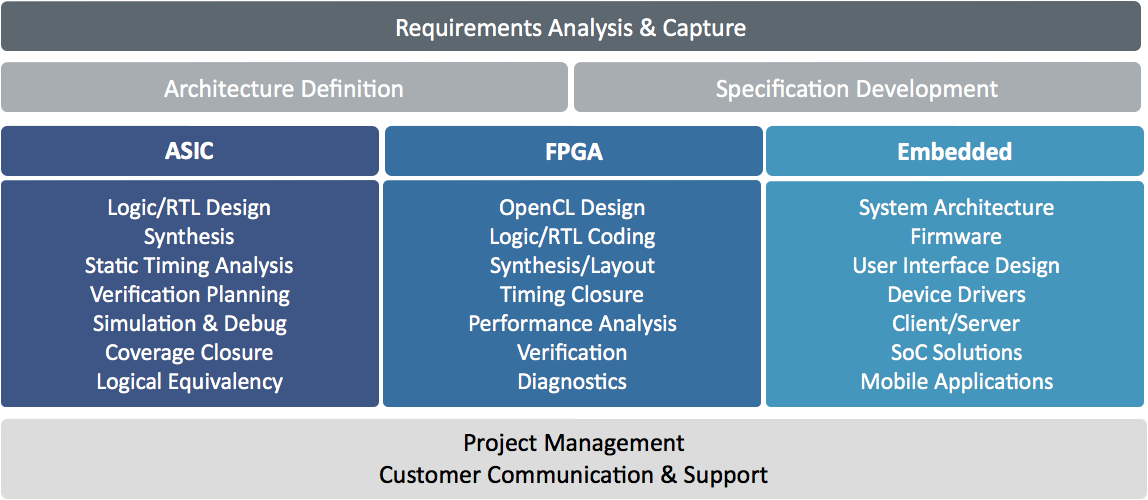

Superion Technology provides an array of critical design skills that are essential to planning, implementation and successful realization of challenging ASIC, FPGA and Embedded System design projects.

Whether your project needs specific individual discipline support, or you require a full team to attack multiple steps in your development cycle, Superion can provide the support that you need with industry-best expertise.

We proudly offer the following development capabilities to our customers:

Technical Approach

If you’re in the mood for some deep reading, the following section provides a detailed description of how we approach a variety of the disciplines we provide. So, grab a cup of coffee and take your time.

We would be happy to talk in greater detail about anything that is missing or needs further clarification.

- Architectural Design and Definition

- Logic/RTL Design

- Design Verification

- Synthesis

- Static Timing Analysis

Whether this means architecture development based on a formal product requirements document, whiteboard brainstorming session or napkin sketch, our team can add value to the very early stages of the overall ASIC development effort.

Working with customer teams to develop the architecture of a block, subsystem or entire chip allows us to better understand the overall context of the entire design. This allows us to be much more efficient in the process of microarchitecture specification and implementation. Understanding the bigger picture enables us to make more informed design decisions and understand the trade-offs faced when choosing implementation strategies.

Drawing from expertise that spans across multiple domains, our team brings a broad array of techniques and strategies to the logic design and coding process. This allows us to adapt and apply the expertise and approach from prior experiences to virtually any type of problem.

RTL coding is done using Verilog and SystemVerilog leveraging the power of SystemVerilog constructs to maximize design modularity, flexibility and partitioning. At the same time, care is taken to ensure that implemented code will be compatible with current versions of CAD tools and development methodologies.

Our design team is very disciplined in the use of assertions and cover properties as part of the design flow. This practice is a key contributor to the design approach employed at Superion. Embedded assertions and cover properties written by the designers directly contributes to the robustness of the verification process and also positions the designs for formal property checking simulations.

For nearly 20 years, our team has approached the verification process with randomized stimulus, self-checking test environments, and modular testbench partitioning. This approach resulted in the most effective isolation of key functionality and top-level chip validation.

Now, with advanced Hardware Verification Languages (HVLs) and methodologies such as the Universal Verification Methodology (UVM), our teams can fully utilize very powerful verification constructs and practices that are being actively developed, supported and enhanced by the greater verification community. Furthermore, our experience with multiple EDA vendors allows us to easily adapt to customer-preferred environments and tool flows.

Our specific experience using Formal Modeling Analysis and Formal Property Checking gives us an edge for designs where functional simulation alone may not provide the robustness and rigor required to ensure a defect free design result.

As part of the physically-aware approach used by our team for design development, we typically leverage physical synthesis tools to generate the netlists that are delivered into the physical design flow.

Once again, using methodologies that consider floorplan, bounding boxes, and the relative physical placement of our design blocks yields optimum synthesis results. This, in turn, provides the most robust possible netlist for PD and reduces iterations required to optimize the design in the final stages of the design flow.

This starts early when timing constraints are developed and checked during early synthesis explorations. These constraints are updated to reflect physical design progress as the project progresses and provide the coupling between logic development and physical implementation. Detailed knowledge and hands-on experience with the timing constraints creates a more efficient review loop between designers and STA engineers during the timing closure process.