A successful verification project requires more than familiarity and experience with the underlying verification methodology. The ability to effectively implement state of the art approaches – such as the Universal Verification Methodology (UVM) – is certainly essential to the verification task. However, UVM is one tool in a much broader scope of required skills, verification process steps, testing techniques and verification project management.

At Superion Technology, we know how to approach the verification challenge. We understand the planning and preparation that is required before a single line of DV code is even considered. We know how to break down the problem and architect a verification solution based on whatever methodology is the best fit for our customer and for the program.

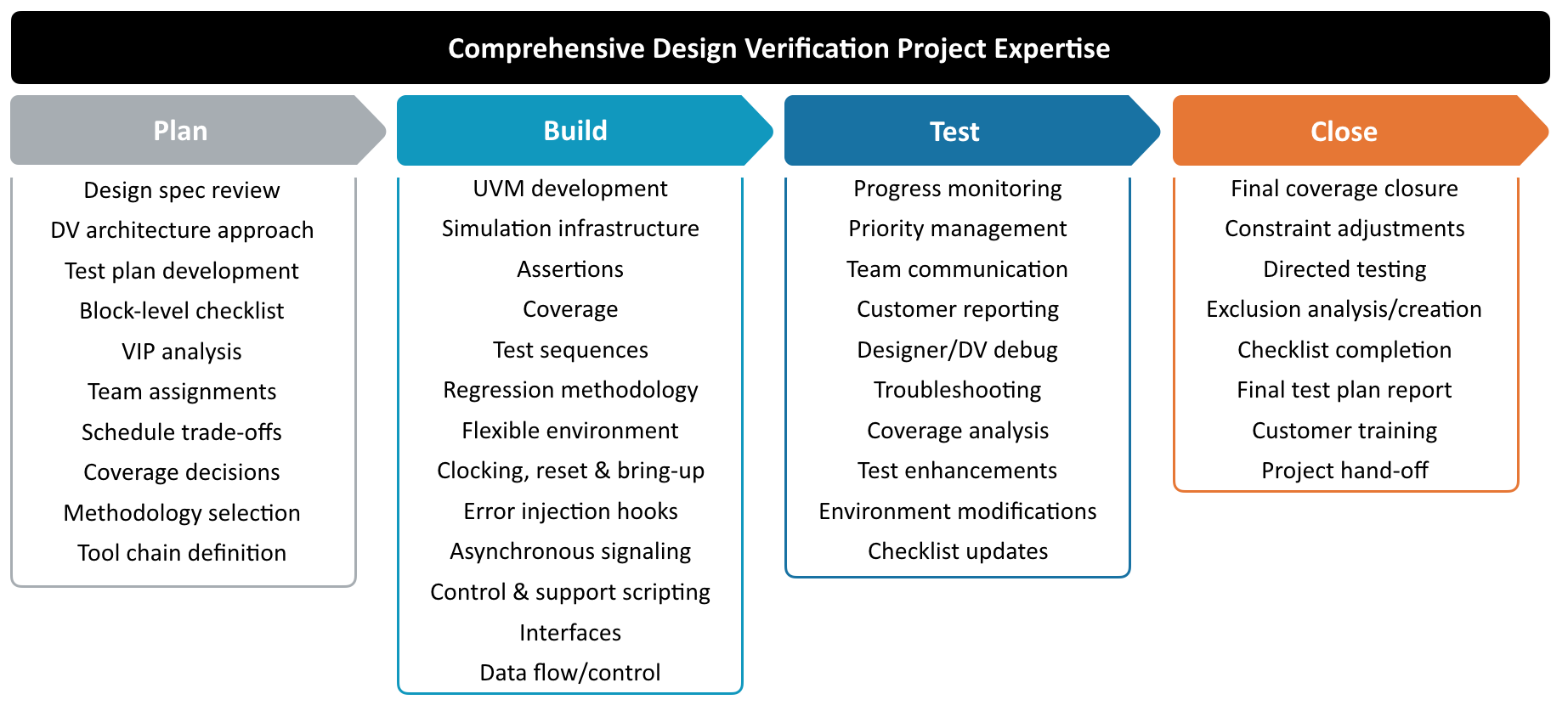

Our experience managing complex verification projects adds value that goes beyond our expertise with implementing UVM and ensures a more comprehensive approach to verifying chip designs. We are pleased to offer the following full-service verification capabilities to our customers.

Approach

- Metric-driven methodology

- Constrained-random stimulus

- Transaction-level modeling

- Functional and code coverage

- Assertions

Methodologies / Languages

- UVM, OVM, VMM, RVM, eRM (Specman)

- SystemVerilog / Verilog 2K

- VHDL

- C, C++, Java, Perl, Tcl, Python

- OpenCL

Tool Experience

- Atrenta Spyglass

- Cadence IES, Conformal

- Mentor ModelSim, Questa

- Synopsys VCS, Formality, Magellan

- Jira, Bugzilla, etc…

- SVN, Git, MKS, Clearcase, others

Want to Learn More?

We would be happy to talk with you about your verification requirements and discuss more about our our approach and experience could be a benefit to your project. Click below to learn more about our verification services offering.